새 도구는 나노미터 트랜지스터에서 결함을 찾는 속도를 높여 공정 디버깅을 더 쉽고 즐겁게 만들 것입니다

현대 반도체에서 원자 결함을 관찰하는 새로운 방법

코넬 대학의 과학자들이 ASM 및 TSMC와 협력하여 최첨단 칩에서 숨겨진 원자 수준의 결함을 시각화할 수 있는 방법을 개발했습니다. 이 접근 방식은 마이크로칩 제조 공정의 디버깅에 특히 중요합니다: 결함을 더 정확하게 평가할수록 불량률이 낮아지고 성숙한 생산에 더 빨리 도달할 수 있습니다.

연구 내용

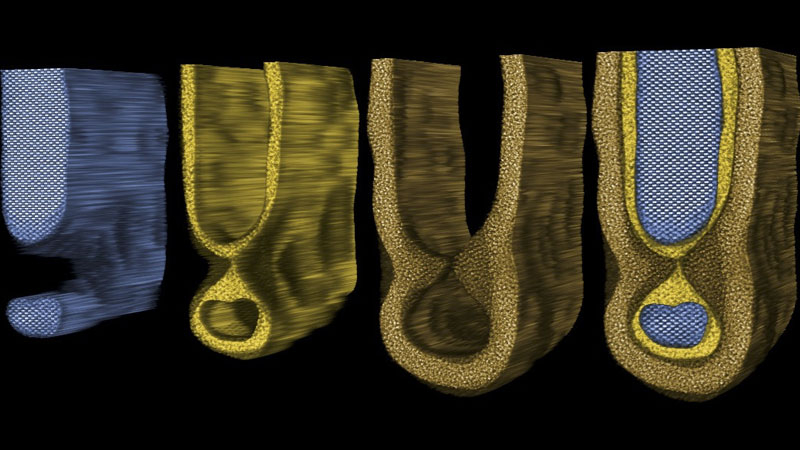

본 연구에서는 Gate‑All‑Around (GAA) 트랜지스터가 장착된 가공 플레이트를 사용했습니다. GAA는 채널을 완전히 둘러싸는 최신 게이트 유형입니다. 벨기에 Imec 센터에서 샘플을 제공했습니다. 각 GAA 채널은 18개의 원자로 구성된 “관” 형태이며, 그 벽면에는 불균일성, 스크래치 및 기타 결함이 있을 수 있어 트랜지스터 특성에 직접적인 영향을 미칩니다. 가공 후 구조를 바꿀 수 없지만 연구자들은 생산 단계마다 수천 번의 절차에서 제조 품질을 추적하여 오류 수를 줄이는 데 성공했습니다.

방법

원자 수준 결함을 관찰하기 위해 과학자들은 다면체 전자 피치아그라피(multislice electron ptychography)를 사용했습니다. 이 방법은 서브앵스트롬, 나노미터 수준의 깊이 해상도를 가진 재료를 제공합니다. 전자 산란을 수집하고 이를 통해 원자 규모 이미지를 만듭니다.

핵심 단계는 STEM(주사 투과형 전자 현미경)에서 EMPAD 검출기를 사용해 4차원 회절 데이터를 수집하는 것입니다. 그런 다음 데이터는 위상 재구성 및 다수의 “슬라이스”를 통한 전자 전달 모델링을 거칩니다. 기존 투영 방법과 달리 피치아그라피는 한 세트 측정에서 전체 부피 구조를 복원하여 개별 원자의 위치, 격자 변형 및 상전이 경계 매개변수를 정확히 결정할 수 있습니다.

효과

- 결함 스펙트럼에 대한 정성적·정량적 평가가 가능해졌습니다. 이전에는 간접적인 방법만 사용되었습니다.

- 개발 초기 단계에서 기술 문제를 빠르게 식별하고 해결할 수 있습니다.

- TSMC와 같은 대형 업체의 관심이 입증된 실용성을 보여줍니다.

따라서 이 새로운 방법은 고기술 반도체 제조 분야에서 보다 신뢰성 있고 효율적인 품질 관리를 가능하게 합니다.

Asted Cloud

Asted Cloud

댓글 (0)

의견을 남겨 주세요. 예의를 지키고 주제에서 벗어나지 말아 주세요.

댓글을 남기려면 로그인