ASML은 내년에 이미 트랜지스터 크기가 1.4nm 이하인 칩을 생산하기 위해 High‑NA EUV 기술의 광범위한 적용을 계획하고 있습니다

새로운 미세화 단계는 고급 리소그래피 기술로의 전환을 요구합니다. 향후 2년 내에 업계는 High‑NA EUV 장비를 사용해 한 번에 8 nm 이하의 크기를 달성하고, 1.4 nm 및 10 nm 미만(DRAM) 공정으로 나아갈 수 있는 기회를 열어줄 것입니다.

1. High‑NA EUV 기술 가능성

파라미터 | 값

수치 조리개 (NA) | 0.55

한 번에 최소 크기 | ≤ 8 nm

가능한 공정 | 1.4 nm(집적 회로), < 10 nm(DRAM)

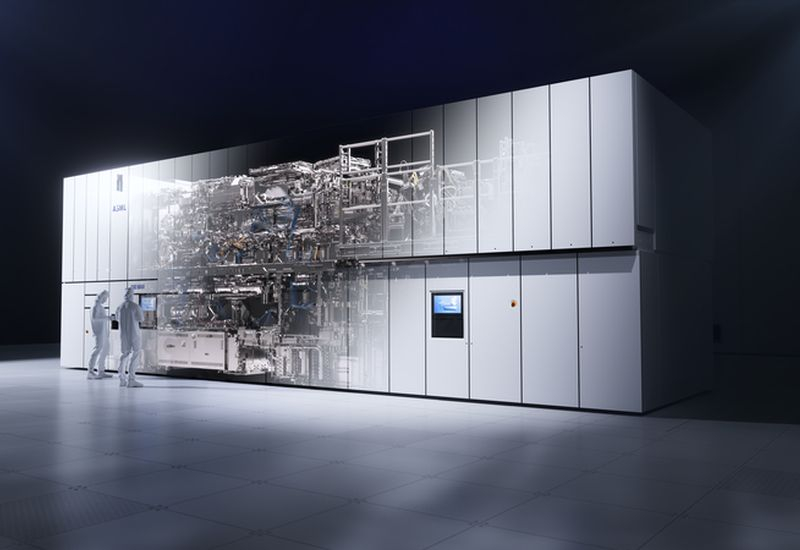

이러한 특성은 ASML Twinscan EXE:5200B 및 유사 솔루션을 향후 마이크로일렉트로닉스 기술에 필수적으로 만듭니다.

2. 주요 플레이어

회사 | 도입 단계 | 비고

ASML | High‑NA EUV 제조업체 | 첫 고객: Intel, Samsung, SK Hynix

TSMC | 대량 사용 준비 중 | 1.4 nm 칩 폐지 계획, 2023년 12월 Twinscan EXE:5200B 도입, 14A 기술 출시 준비

Samsung Electronics | 첫 스캐너를 2023년 12월 획득, 두 번째는 이번 반기, Exynos 2600(2 nm) 및 향후 Tesla 프로세서에 사용 예정

SK Hynix | 2023년 9월부터 High‑NA EUV 활용 시작, 현재 DRAM(10 nm)에서 일반 EUV를 사용 중, 6세대에 최소 다섯 개 EUV 레이어 계획

Micron Technology | 도입 시점 미정

Rapidus (일본) | 2 nm 기술 습득, 2029년 1.4 nm 목표, 2027년에는 홋카이도에서 2 nm 칩 대량 생산 시작 예정

3. 경제적 측면

* 장비 비용 – High‑NA EUV 한 시스템 약 3억 8천만 USD.

* 더 비싼 장비로 전환하면 제품 원가 상승, 최종적으로 소비자 가격에 반영.

* 따라서 TSMC, Rapidus 같은 대형 제조업체는 신중하게 접근하며 단계별 도입을 계획.

4. 예상 일정

High‑NA EUV를 활용한 ASML의 새로운 리소그래피 스캐너는 2027–2028년 사이에 첨단 반도체 제품의 대량 생산에 적극적으로 사용될 전망입니다. 그 전까지 기업들은 기존 공정에 High‑NA EUV를 통합하며 점진적으로 라인 조정을 진행할 것입니다.

결론

High‑NA EUV 도입은 1.4 nm 이하 및 더 작은 DRAM 실현을 위한 핵심 단계입니다. 세계 최대 업체들이 이미 준비 작업을 시작했지만, 높은 비용과 생산 체계 적응 필요성으로 인해 대규모 적용은 몇 년 후에야 가능할 것으로 보인다.

Asted Cloud

Asted Cloud

댓글 (0)

의견을 남겨 주세요. 예의를 지키고 주제에서 벗어나지 말아 주세요.

댓글을 남기려면 로그인